Sin embargo, sigue siendo necesario el tener algunas nociones así sea elementales de electricidad y electrónica para evitar incurrir en errores y equivocaciones con las cuales podemos terminar creando un sistema inestable propenso inclusive a fallos mayores.

Para la transmisión simultánea de ocho bits de información, considérense ocho alambres de cobre que serán usados como conductores de electricidad, dispuestos en un arreglo paralelo horizontal como se muestra a continuación, a los cuales queremos conectar cada una de las ocho terminales de algún dispositivo (un disco duro, una escaneadora, un sistema de sonido, etc.). La siguiente figura nos muestra a un dispositivo tal conectado a los ocho alambres de cobre, transmitiendo a través de los mismos la palabra binaria 10010100:

Los ocho alambres de cobre a lo largo de los cuales se transmite la información binaria enviada por el dispositivo, tomados en conjunto son referenciados como el bus de datos, el “canal” de conducción de los datos que estarán siendo enviados por el dispositivo en cuestión.

Supóngase ahora que, para no hacer un gasto superfluo en alambrado y ahorrar al mismo tiempo una buena cantidad de espacio, queremos utilizar esos mismos ocho alambres de cobre, ese mismo bus de datos, para que un segundo dispositivo pueda enviar sus propios datos a través del mismo bus:

Veamos lo que sucede si conectamos las terminales de ambos dispositivos al bus de datos:

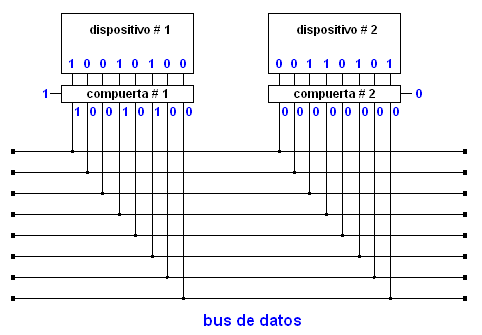

Si queremos hacer tal cosa, de inmediato vemos que tenemos un problema. El primer dispositivo quiere enviar a través de los ocho alambres de cobre la palabra binaria 100010100 mientras que el segundo dispositivo quiere enviar a través de los mismos ocho alambres de cobre la palabra binaria 00110101. Esto conlleva a un conflicto importante. Si en cierto alambre de cobre un dispositivo está depositando un “1” mientras que en el mismo alambre de cobre el otro dispositivo quiere depositar un “0”, ¿cuál valor deberá tomar el alambre de cobre?

Un primer intento de solventar el conflicto consiste en colocar compuertas (conocidas en la literatura técnica inglesa como gates) a la salida de cada dispositivo, construídas usando bloques AND:

Si hacemos esto ingenuamente, entonces para dejar pasar la información binaria del primer dispositivo a los alambres de cobre pondríamos un “1” en la terminal ABRIR de la compuerta que puede permitir o bloquear el paso de la información binaria del primer dispositivo hacia los alambres de cobre, mientras que pondríamos un “0” en la terminal ABRIR de la compuerta que puede permitir o bloquear el paso de la información binaria del segundo dispositivo hacia los alambres de cobre. En una situación así, la compuerta del primer dispositivo permitiría el paso de la información binaria mientras que la compuerta del segundo dispositivo la bloquearía:

Sin embargo, seguimos teniendo el mismo conflicto que teníamos anteriormente, solo hemos dado un paso modesto hacia la solución del problema. Pero más grave aún, si analizamos la situación desde la perspectiva en que la ven los que se especializan en el comportamiento electrónico del sistema, se tiene aquí una receta para un desastre. En efecto, recordemos que un “0” puede representar la ausencia de un voltaje mientras que un “1” puede representar la presencia de un voltaje, digamos un voltaje positivo de 5 voltios. Sin embargo, un “0” no implica que no haya “nada”, eléctricamente hablando. De hecho, un “0” viene siendo necesariamente el polo negativo de la batería o de la fuente de poder con la que trabaja el sistema. El “0” implica que, eléctricamente hablando, lo que tiene puesto un “0” está conectado al polo negativo o “tierra” eléctrica del sistema (el uso de la palabra “tierra” puede provocar confusiones, ya que en los diagramas esquemáticos de los circuitos electrónicos no tiene nada que ver con la “tierra” en la que sembramos flores y árboles, es simplemente un conjunto común conectado eléctricamente al polo negativo de la batería). En una batería de uso casera, la terminal positiva y la terminal negativa son un concepto muy familiar:

En los diagramas esquemáticos, el símbolo universal de una batería o inclusive de una fuente de poder cualquiera es el siguiente:

¿Y qué sucede cuando conectamos en forma directa con un alambre conductor de electricidad (un alambre de cobre) el polo negativo de una batería (que viene siendo el equivalente del “0” lógico) al polo positivo de la batería (que viene siendo el equivalente del “1” lógico)? Teniendo el alambre conductor una resistencia eléctrica casi igual a cero, de acuerdo a la ley de Ohm bajo cierto voltaje como los que estamos considerando se produce una corriente eléctrica sumamente grande que en menos de un segundo puede destruír a la batería, porque se produce la condición que todos conocemos como un corto circuito. Esta es la causa de muchos incendios en viviendas con instalaciones eléctricas defectuosas.

Regresando a los dos dispositivos conectados a los alambres de cobre mediante el uso de compuertas, vemos que se producen tres cortos circuitos, siendo el primero de ellos el siguiente (se ha destacado en color rojo el corto circuito que se produce):

Tenemos además los siguientes cortocircuitos:

En otros tiempos, cuando la electrónica estaba basada en tubos electrónicos o en transistores individuales, algo como esto podría haber quemado el prototipo del sistema o tal vez causar un incendio. Afortunadamente, los circuitos integrados actuales no son tan propensos a desastres de este tipo. Sin embargo, persiste el conflicto de cómo conectar dos dispositivos distintos a un mismo bus de datos. Podríamos, en todo caso, conectar la salida de cada compuerta a una compuerta en la que cada par de terminales fuera a dar a un circuito OR que permitiría la salida de la palabra binaria no-bloqueada, sin ocasionar cortocircuitos. Sin embargo, el tener que meter este tipo de arreglo complicaría enormemente el concepto de poder conectar y desconectar aparatos de todo tipo a un bus común de datos sin tener que andar intercalando más dispositivos lógicos en la red de alambres al hacer tal cosa.

La salida del dilema consiste en recurrir a lo que se conoce como lógica de tres estados (tri-state logic, en literatura técnica inglesa). En su concepción más elemental, esto consiste en recurrir a un interruptor ordinario del modo siguiente:

Bajo este esquema, si la entrada HABILITAR (Enable) es activada con un “1” lógico, entonces la ENTRADA está conectada eléctricamente en forma directa a la terminal de SALIDA. Si deshabilitamos al terminal de HABILITAR poniéndole un “0” lógico, entonces la ENTRADA queda desconectada eléctricamente de la terminal de salida. El símbolo triangular que vemos arriba en la parte inferior es una representación usada frecuentemente en los diagramas esquemáticos para denotar el bloque de tres estados.

Bajo la lógica de los tres estados, tenemos entonces las siguientes tres posibilidades:

Si la terminal HABILITAR tiene puesto un “1”, entonces un “1” en la terminal de ENTRADA pasará directamente como un “1” a la terminal de SALIDA, y un “0” en la terminal de ENTRADA pasará como un “0” a la terminal de salida. Pero con un “0” puesto en la terminal HATILITAR, no pasará nada de la terminal de ENTRADA a la terminal de SALIDA, habiendo en efecto una desconexión eléctrica total (en la práctica, al implementar esta función en circuitos integrados, la desconexión no es total, pero se pone una resistencia -o impedancia- sumamente elevada entre la terminal de ENTRADA y la terminal de salida, por ejemplo de 10 Megohms, que para fines prácticos hay una desconexión eléctrica real). De este modo, con esta técnica a nuestra disposición, y usando ocho bloques tri-state para construír cada compuerta (en lugar de los bloques AND originales) teniendo algo como lo siguiente:

podemos ver la manera en la cual cada dispositivo puede ir depositando sus datos en el bus de datos sin riesgo de que se produzca un corto circuito:

Obviamente, para que esto pueda funcionar, se vuelve requisito indispensable que en ningún momento las terminales de activación HABILITAR de ambas compuertas estén “encendidas” con un “1”, porque si esto ocurre volveríamos al problema que hemos querido evitar. ¿Yqué se encarga de que no haya conflictos de este tipo, de que todo marche en forma sincronizada? El bloque de circuitos de control situado dentro de la unidad de procesamiento central CPU de la computadora, desde luego.

El último gráfico nos haría suponer erróneamente que esas ocho líneas serían suficientes para enviar las señales eléctricas de unos y ceros de palabras binarias de ocho bits al bus de datos. Pero en realidad, se requiere otra línea de conducción eléctrica, la línea de tierra para permitir el regreso de la corriente eléctrica al polo negativo de la fuente de poder. Esta línea debe estar presente y conectada físicamente todo el tiempo a los dos dispositivos que se muestran arriba:

En realidad, físicamente hablando, ninguno de los dispositivos está realmente desconectado a las líneas de conducción del bus de datos. La desconexión es eléctrica, con la ayuda de la lógica de tres estados, no mecánica. Cuando conectamos una impresora o una escaneadora a la computadora, la conexión permanece hasta que la sesión se da por terminada.

La lógica de tres estados tri-state no sólo sirve para conectar en forma alternada la salida de varios dispositivos a un bus común. También es utilizada en el interior del diseño de los microprocesadores para el enrutamiento de datos hacia conjuntos comunes de líneas de transmisión eléctrica, además de usarse en la construcción de varios circuitos integrados que suelen ser aplicados en diseños de maquinaria de control y automatización digital de procesos. Uno de tales circuitos integrados, fabricado con tecnología MOS (Metal-Oxide-Semiconductor), es el “chip” 4048, una compuerta tri-state expandible de ocho entradas y ocho funciones cuyo diagrama es el siguiente:

El componente incorpora tres líneas de control Ka, Kb y Kc, que determinan las ocho diferentes funciones lógicas de la compuerta. Una cuarta entrada, Kd, es la que actúa como el control de la lógica de tres estados. Mientras a esta entrada Kd se le esté suministrando un “1”, las salida J de la compuerta seguirá apareciendo en la terminal 1 del chip. Si la cuarta entrada Kd deja de ser activada poniéndole un “0”, entonces la salida J “flotará” quedando eléctricamente desconectada del punto hacia el cual está unida físicamente en forma permanente, correspondiendo la función de salida a una impedancia alta. Esta propiedad permite conectar la salida J del circuito integrado a una línea de bus común. La línea de expansión en la terminal 15 le permite al diseñista incrementar el número de entradas de compuerta. Dos circuitos 4048 de ocho entradas cada uno, por ejemplo, se pueden conectar en cascada para formar una compuerta multifuncional de 16 entradas. Cuando la entrada de expansión no es utilizada, debe ser conectada al polo Vss de la fuente de poder. La tabla de verdad para el circuito integrado 4048 se muestra a continuación:

| Función de salida |

Expresión Boleana | Entradas de control |

|||

| Ka | Kb | Kc | Kd | ||

NOR . |

J = A+B+C+D+E+F+G+H . |

0 | 0 | 0 | 1 |

| OR | J = A+B+C+D+E+F+G+H | 0 | 0 | 1 | 1 |

| OR/AND | J = (A+B+C+D)·(E+F+G+H) | 0 | 1 | 0 | 1 |

OR/NAND . |

J = (A+B+C+D)·(E+F+G+H) | 0 | 1 | 1 | 1 |

| AND | J = A·B·C·D·E·F·G·H | 1 | 0 | 0 | 1 |

NAND . |

J = A·B·C·D·E·F·G·H | 1 | 0 | 1 | 1 |

AND/NOR . |

J = (A·B·C·D)+(E·F·G·H) | 1 | 1 | 0 | 1 |

| AND/OR | J = (A·B·C·D)+(E·F·G·H) | 1 | 1 | 1 | 1 |

| Impedancia alta |

X | X | X | 0 | |

PROBLEMA: Partiendo de una memoria RAM capaz de poder almacenar 256 palabras binarias de 4-bits, con entradas y salidas separadas, diseñar una memoria de la misma capacidad pero que tenga una entrada y una salida común, esto es, que tanto los datos leídos como los datos a ser almacenados en la memoria puedan ser tomados y depositados en el mismo bus bi-direccional.

La memoria RAM básica, con entradas y salidas separadas, debe tener un aspecto como el siguiente:

En el diagrama, la línea identificada como:

LEER/ESCRIBIR

es usada con frecuencia en los diagramas esquemáticos aunque es rara la vez en la cual se le dá una explicación. Para entender este tipo de notación, supóngase que a la terminal se le aplica un “0” lógico. Entonces esto equivale a afirmar:

LEER/ESCRIBIR = 0

y se puede interpretar de dos maneras, ya sea como:

LEER = 0

o como:

ESCRIBIR = 0

Esto último es lo mismo que:

ESCRIBIR = 1

O sea que con un “0” puesto en la terminal LEER/ESCRIBIR se desactiva con un “0” la capacidad de poder leer los datos almacenados en la memoria RAM y se activa con un “1” (como consecuencia de la lógica negativa o complementaria) la capacidad para poder escribir datos hacia la memoria RAM, y Ambas capacidades son complementarias, ya que no se puede leer y escribir al mismo tiempo a una memoria de acceso aleatorio, y por esto mismo se pueden obtener ambas acciones con una sola terminal de entrada (en lugar de dos entradas separadas LEER y ESCRIBIR que normalmente se usarían de modo independiente). Del mismo modo, con:

LEER/ESCRIBIR = 1

se activa la memoria RAM para que sus contenidos puedan ser leídos en las líneas Out1, Out2, Out3 y Out4, impidiéndose que se pueda poner dato alguno en el RAM mediante las líneas de entrada In1, In2, In3 e In4.

La memoria RAM dada arriba tiene entradas y salidas independientes, y puede ser usada en un sistema en el que haya un bus de datos de entrada en el cual los datos únicamente pueden ser depositados en dicho bus, y otro bus de datos de salida del cual únicamente se pueden tomar datos. Si queremos recortar a la mitad el número de líneas de conducción eléctrica para tomar y depositar datos, especificamos un bus bi-direccional, lo cual a su vez requiere que los dispositivos conectados al mismo puedan ser manipulados con lógica tri-state de tres estados. La manera de lograrlo es añadiendo compuertas al RAM que tenemos arriba, una compuerta de entrada y una compuerta de salida, del modo siguiente:

Poniendo un “1” en la terminal LEER/ESCRIBIR abre la compuerta de salida tri-state, permitiendo el depósito en el bus bi-direccional de los datos leídos del RAM, lo cual a su vez pone un “0” (por la acción del NOT inversor) en el “gatillo” de la compuerta de entrada que hace que la entrada de datos al RAM sea desconectada por completo (eléctricamente hablando) del bus bi-direccional. Por otro lado, poniendo un “0” en la terminal LEER/ESCRIBIR abre la compuerta de entrada, permitiendo el depósito en el RAM de los datos que pueda haber en el bus bi-direccional, lo cual a su vez pone un “1” (por acción del NOT inversor) en el “gatillo” de la compuerta de entrada que hace que la entrada al RAM sea conectada (eléctricamente hablando) al bus bi-direccional, permitiendo con ello el depósito de los datos que haya en el bus bi-direccional de datos al interior de la memoria RAM. Obsérvese que únicamente la compuerta de salida (usada internamente por el RAM en un circuito integrado diseñado para tales efectos) tiene que ser una compuerta de tres estados, la compuerta de entrada puede ser una compuerta ordinaria usando funciones lógicas AND ordinarias para llevar a cabo el bloqueo de datos.

Es muy importante resaltar que en mucha literatura técnica, en lugar de simbolizarse la activación (con un “1”) o la desactivación (con un “0”) de dicha terminal para las funciones de lectura o escritura con la notación:

LEER/ESCRIBIR

también es frecuente encontrar que dicha terminal sea simbolizada simplemente como:

LEER/ESCRIBIR

entendiéndose que, como no es posible llevar a cabo al mismo tiempo la función de escritura hacia el RAM y la función de escritura hacia el RAM, dicha terminal puede alternar entre una función y otra dependiendo del valor lógico que le sea aplicado a dicha terminal.

Lo que acabamos de ver no es tan teórico y académico como algunos pudieran suponer. Existe una memoria RAM fabricada con tecnología MOS, el chip 2101, que es precisamente una memoria RAM estática 256×4 con entradas y salidas independientes. Con la adición de la lógica tri-state, de esta misma memoria RAM se obtiene otra, el chip 2111, que también es una memoria RAM estática 256×4 pero con una entrada/salida común, diseñada específicamente para ser usada con un bus-bidireccional de datos. La acción de compuerta lógica de tres estados puede ser obtenida con varios circuitos integrados disponibles comercialmente, tales como el circuito integrado 4066 (el cual puede ser usado como un interruptor de dos vías no solo para el enrutamiento de señales digitales sino también de señales analógicas, habiendo cuatro interruptores tales en este circuito integrado):

Este circuito integrado es eléctricamente similar (y compatible físicamente en lo que a cada una de las terminales respecta) con el circuito integrado 4016, excepto que el circuito integrado 4066 es una versión mejorada del circuito integrado 4016 con una resistencia de contacto entre las terminales de cada interruptor (90 ohms) menor que la resistencia de contacto entre las terminales de cada interruptor del 4016 (300 ohms).